Contains CCxxxx register and bitfield values See Registers: Normal, Registers: Status, Registers: Multibyte, Registers: Strobe Command. More...

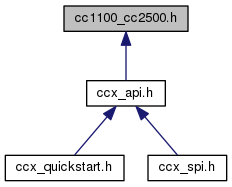

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Macros | |

| #define | CCX_REG_IOCFG2 0x00 |

| GDO2 output pin configuration. | |

| #define | CCX_REG_IOCFG1 0x01 |

| GDO1 output pin configuration. | |

| #define | CCX_REG_IOCFG0 0x02 |

| GDO0 output pin configuration. | |

| #define | CCX_REG_FIFOTHR 0x03 |

| RX FIFO and TX FIFO thresholds. | |

| #define | CCX_REG_SYNC1 0x04 |

| Sync word, high byte. | |

| #define | CCX_REG_SYNC0 0x05 |

| Sync word, low byte. | |

| #define | CCX_REG_PKTLEN 0x06 |

| Packet length. | |

| #define | CCX_REG_PKTCTRL1 0x07 |

| Packet automation control. | |

| #define | CCX_REG_PKTCTRL0 0x08 |

| Packet automation control. | |

| #define | CCX_REG_ADDR 0x09 |

| Device address. | |

| #define | CCX_REG_CHANNR 0x0A |

| Channel number. | |

| #define | CCX_REG_FSCTRL1 0x0B |

| Frequency synthesizer control. | |

| #define | CCX_REG_FSCTRL0 0x0C |

| Frequency synthesizer control. | |

| #define | CCX_REG_FREQ2 0x0D |

| Frequency control word, high byte. | |

| #define | CCX_REG_FREQ1 0x0E |

| Frequency control word, middle byte. | |

| #define | CCX_REG_FREQ0 0x0F |

| Frequency control word, low byte. | |

| #define | CCX_REG_MDMCFG4 0x10 |

| Modem configuration. | |

| #define | CCX_REG_MDMCFG3 0x11 |

| Modem configuration. | |

| #define | CCX_REG_MDMCFG2 0x12 |

| Modem configuration. | |

| #define | CCX_REG_MDMCFG1 0x13 |

| Modem configuration. | |

| #define | CCX_REG_MDMCFG0 0x14 |

| Modem configuration. | |

| #define | CCX_REG_DEVIATN 0x15 |

| Modem deviation setting. | |

| #define | CCX_REG_MCSM2 0x16 |

| Main Radio Control State Machine configuration. | |

| #define | CCX_REG_MCSM1 0x17 |

| Main Radio Control State Machine configuration. | |

| #define | CCX_REG_MCSM0 0x18 |

| Main Radio Control State Machine configuration. | |

| #define | CCX_REG_FOCCFG 0x19 |

| Frequency Offset Compensation configuration. | |

| #define | CCX_REG_BSCFG 0x1A |

| Bit Synchronization configuration. | |

| #define | CCX_REG_AGCCTRL2 0x1B |

| AGC control. | |

| #define | CCX_REG_AGCCTRL1 0x1C |

| AGC control. | |

| #define | CCX_REG_AGCCTRL0 0x1D |

| AGC control. | |

| #define | CCX_REG_WOREVT1 0x1E |

| High byte Event 0 timeout. | |

| #define | CCX_REG_WOREVT0 0x1F |

| Low byte Event 0 timeout. | |

| #define | CCX_REG_WORCTRL 0x20 |

| Wake On Radio control. | |

| #define | CCX_REG_FREND1 0x21 |

| Front end RX configuration. | |

| #define | CCX_REG_FREND0 0x22 |

| Front end TX configuration. | |

| #define | CCX_REG_FSCAL3 0x23 |

| Frequency synthesizer calibration. | |

| #define | CCX_REG_FSCAL2 0x24 |

| Frequency synthesizer calibration. | |

| #define | CCX_REG_FSCAL1 0x25 |

| Frequency synthesizer calibration. | |

| #define | CCX_REG_FSCAL0 0x26 |

| Frequency synthesizer calibration. | |

| #define | CCX_REG_RCCTRL1 0x27 |

| RC oscillator configuration. | |

| #define | CCX_REG_RCCTRL0 0x28 |

| RC oscillator configuration. | |

| #define | CCX_REG_FSTEST 0x29 |

| Frequency synthesizer calibration control. | |

| #define | CCX_REG_PTEST 0x2A |

| Production test. | |

| #define | CCX_REG_AGCTEST 0x2B |

| AGC test. | |

| #define | CCX_REG_TEST2 0x2C |

| Various test settings. | |

| #define | CCX_REG_TEST1 0x2D |

| Various test settings. | |

| #define | CCX_REG_TEST0 0x2E |

| Various test settings. | |

| #define | CCX_REG_STROBE_SRES 0x30 |

| Reset chip. | |

| #define | CCX_REG_STROBE_SFSTXON 0x31 |

| Enable and calibrate frequency synthesizer. | |

| #define | CCX_REG_STROBE_SXOFF 0x32 |

| Turn off crystal oscillator. | |

| #define | CCX_REG_STROBE_SCAL 0x33 |

| Calibrate frequency synthesizer and turn it off. | |

| #define | CCX_REG_STROBE_SRX 0x34 |

| Enable RX. | |

| #define | CCX_REG_STROBE_STX 0x35 |

| Enable TX. | |

| #define | CCX_REG_STROBE_SIDLE 0x36 |

| Exit RX/TX. | |

| #define | CCX_REG_STROBE_SWOR 0x38 |

| Start automatic RX polling sequence. | |

| #define | CCX_REG_STROBE_SPWD 0x39 |

| Enter power down mode when CSn goes high. | |

| #define | CCX_REG_STROBE_SFRX 0x3A |

| Flush the RX FIFO buffer. | |

| #define | CCX_REG_STROBE_SFTX 0x3B |

| Flush the TX FIFO buffer. | |

| #define | CCX_REG_STROBE_SWORRST 0x3C |

| Reset real time clock to Event1 value. | |

| #define | CCX_REG_STROBE_SNOP 0x3D |

| No operation. | |

| #define | CCX_REG_STATUS_PARTNUM 0x30 |

| Part number. | |

| #define | CCX_REG_STATUS_VERSION 0x31 |

| Current version number. | |

| #define | CCX_REG_STATUS_FREQEST 0x32 |

| Frequency offset estimate. | |

| #define | CCX_REG_STATUS_LQI 0x33 |

| Demodulator estimate for link quality. | |

| #define | CCX_REG_STATUS_RSSI 0x34 |

| Received signal strength indication. | |

| #define | CCX_REG_STATUS_MARCSTATE 0x35 |

| Control state machine state. | |

| #define | CCX_REG_STATUS_WORTIME1 0x36 |

| High byte of WOR timer. | |

| #define | CCX_REG_STATUS_WORTIME0 0x37 |

| Low byte of WOR timer. | |

| #define | CCX_REG_STATUS_PKTSTATUS 0x38 |

| Current GDOx status and packet status. | |

| #define | CCX_REG_STATUS_VCO_VC_DAC 0x39 |

| Current setting from PLL cal module. | |

| #define | CCX_REG_STATUS_TXBYTES 0x3A |

| Underflow and # of bytes in TXFIFO. | |

| #define | CCX_REG_STATUS_RXBYTES 0x3B |

| Overflow and # of bytes in RXFIFO. | |

| #define | CCX_MARCSTATE_GET_STATE(_MS) CCX_GET_BITS_VALUE((_MS), 5, 0) |

| Retrives the value of the Main Radio Control FSM state. More... | |

| #define | CCX_MARCSTATE_IS_IN_TX(_MS) |

| Determines if the Main Radio Control FSM state is transmit mode. More... | |

| #define | CCX_PKTSTATUS_GET_CRC_OK(_PS) CCX_GET_BITS_VALUE((_PS), 1, 7) |

| Obtain CRC_OK from contents of the Packet Status register. More... | |

| #define | CCX_PKTSTATUS_GET_PQT_REACHED(_PS) CCX_GET_BITS_VALUE((_PS), 1, 5) |

| Obtain PQT_REACHED from contents of the Packet Status register. More... | |

| #define | CCX_PKTSTATUS_GET_PQT_REACHED(_PS) CCX_GET_BITS_VALUE((_PS), 1, 5) |

| Obtain PQT_REACHED from contents of the Packet Status register. More... | |

| #define | CCX_PKTSTATUS_GET_CCA(_PS) CCX_GET_BITS_VALUE((_PS), 1, 4) |

| Obtain CCA from contents of the Packet Status register. More... | |

| #define | CCX_PKTSTATUS_GET_SFD(_PS) CCX_GET_BITS_VALUE((_PS), 1, 3) |

| Obtain SDF from the contents of the Packet Status register. More... | |

| #define | CCX_PKTSTATUS_GET_GDO2(_PS) CCX_GET_BITS_VALUE((_PS), 1, 2) |

| Obtain GDO2 from the contents of the Packet Status register. More... | |

| #define | CCX_PKTSTATUS_GET_GDO0(_PS) CCX_GET_BITS_VALUE((_PS), 1, 0) |

| Obtain GDB0 from the contents of the Packet Status register. More... | |

| #define | CCX_TX_FIFO_MAX 64 |

| The size, in bytes, of the Transmit FIFO. | |

| #define | CCX_TX_BYTES_IS_UNDERFLOW(_TX) CCX_GET_BITS_VALUE(_TX, 1, 7) |

| Obtain TXFIFO_UNDERFLOW from a prior reading of the TX Underflow and Number of bytes register. More... | |

| #define | CCX_TX_BYTES_IN_FIFO(_TX) CCX_GET_BITS_VALUE(_TX, 7, 0) |

| Obtain NUM_TXBYTES from a prior reading of TX Underflow and Number of bytes register. More... | |

| #define | CCX_RX_FIFO_MAX 64 |

| The size, in bytes, of the Receive FIFO. | |

| #define | CCX_RX_BYTES_IS_OVERFLOW(_RX) CCX_GET_BITS_VALUE(_RX, 1, 7) |

| Obtain RXFIFO_OVERFLOW from a prior reading of Rx Overflow and Number of bytes register. More... | |

| #define | CCX_RX_BYTES_IN_FIFO(_RX) CCX_GET_BITS_VALUE(_RX, 7, 0) |

| Obtain NUM_RXBYTES from a prior reading of RX Underflow and Number of bytes register. More... | |

| #define | CCX_REG_MULTIBYTE_PATABLE 0x3E |

| PA Power Control Settings. | |

| #define | CCX_REG_MULTIBYTE_TXFIFO 0x3F |

| Transmit FIFO (write access) | |

| #define | CCX_REG_MULTIBYTE_RXFIFO 0x3F |

| Receive FIFO (read addcess) | |

| #define | CCX_MASK(_WIDTH, _OFFSET) (((2<<(_WIDTH - 1)) - 1) << (_OFFSET)) |

| Create a bit nask. More... | |

| #define | CCX_GET_BITS_VALUE(_BITFIELD, _WIDTH, _OFFSET) (((_BITFIELD) & (CCX_MASK(_WIDTH, _OFFSET))) >> _OFFSET) |

| Retrive a bit mask from a variable. The value will be shifted so that it occupies the least significant bytes. More... | |

| #define | CCX_HEADER_READ CCX_MASK(1,7) |

| Mask of the Read bit within the header byte. | |

| #define | CCX_HEADER_BURST CCX_MASK(1,6) |

| Mask of the Burst bit within the header byte. | |

| #define | CCX_HEADER_ADDRESS CCX_MASK(6,0) |

| Mask of the Address bits within the header byte. | |

| #define | CCX_SB_GET_STATE(_SB) CCX_GET_BITS_VALUE(_SB, 3, 4) |

| Retrieves the current main state machine mode from the Chip Status byte. | |

| #define | CCX_SB_GET_FIFO_BYTES_AVAILABLE(_SB) CCX_GET_BITS_VALUE(_SB, 4, 0) |

| Retrieves the current bytes available in the RX FIFO / TX FIFO depending on if the Chip Status byte was retrieved during a Read/Write operation. | |

| #define | CCX_APD_B0_GET_RSSI(_BYTE0) (_BYTE0) |

| Retrieves the RSSI value which is present within the first optional status byte, appended to received data. More... | |

| #define | CCX_APD_B1_IS_CRC_OK(_BYTE1) ((_BYTE1) & CCX_MASK(1,7)) |

| Retrieves CRC check value which is present within the second optional status byte, appended to received data. More... | |

| #define | CCX_APD_B1_GET_LQI(_BYTE1) (CCX_GET_BITS_VALUE((_BYTE1),7,0)) |

| Retrieves Link Quality Indication value, which is present within the second optional status byte, appended to received data. More... | |

Detailed Description

Contains CCxxxx register and bitfield values See Registers: Normal, Registers: Status, Registers: Multibyte, Registers: Strobe Command.

Values obtained from datasheet "CC1101 Low-Power Sub-1 GHz RF Transceiver", "TI", "SWRS061".

1.8.13

1.8.13